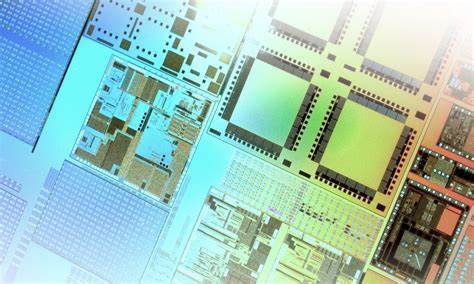

RTL: Synthesis and Physical Design

Dive into the world of digital RTL design with Verilog and physical synthesis, covering everything from HDL coding to ASIC and FPGA verification. Pre-requisites include foundational electronics and digital logic design courses.

Course Contents

- •Digital RTL Design Flow Introduction

- •Basics of ASICs and FPGAs

- •HDL Coding (Verilog)

- •State Machine Design

- •HDL Test-bench Design

- •RTL Code Compilation Scripts Development

- •Synthesizable RTL

- •Detailed RTL Synthesis

- •Verification (ASIC tools & FPGAs) & Test Benches

- •RTL Logic Synthesis Using 130 or 65nm CMOS PDK

- •Static Timing Analysis

- •Design Import Export & Floorplan

- •Design Placement, Clock Tree Synthesis, and Routing

- •PAD Frame and I/O

- •Chip Finishing & Signoff

Lab Topics

- •Introduction to Verilog HDL Coding

- •Designing State Machines in Verilog

- •Writing and Using HDL Test-benches

- •RTL Code Compilation and Scripting

- •Synthesis of RTL Code

- •Verification of Synthesized RTL on ASIC and FPGA Tools

- •Static Timing Analysis

- •Floorplanning and Design Import/Export

- •Placement, Clock Tree Synthesis, and Routing

- •LEF Generation, PAD Frame, and I/O Design

- •Chip Finishing and Signoff

- •Complete RTL Design and Synthesis Project

Course Learning Outcomes

- •Understand the RTL design flow and its importance in digital circuit design.

- •Write and optimize Verilog HDL code for synthesizable RTL designs.

- •Perform static timing analysis and verify RTL designs using ASIC and FPGA tools.

- •Implement and optimize state machines, clock trees, and PAD frames in RTL synthesis.

- •Complete a chip finishing and signoff process for RTL designs.